SocLib Components General Index

Mapping

1) Functional Description

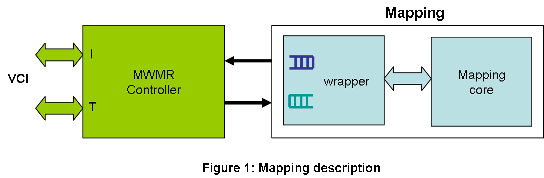

The mapping operation consists in modulating the inputs bits into symbols (complex signals). In our system, the used mapping is a QPSK (Quadrature Phase-Shift Keying) modulation. This means each symbol is coded by two bits. The architecture of the mapping component is presented in the figure 1. It is composed of a mapping core and a MWMR wrapper. The wrapper is used to interface the core and the MWMR controller avalaible here VciMwmrController.

2) CABA Implementation

a) Component definition & usage

Component definition

Usage

Mapping has a fifo_depth parameter, which defines the fifo depth for the input. For example with a FIFO depth equal to 16 :

Uses('Mapping', fifo_depth = 16);

b) CABA sources

- interface : source:trunk/soclib/soclib/module/ofdm_chain_components/mapping/caba/source/include/mapping.h

- implementation : source:trunk/soclib/soclib/module/ofdm_chain_components/mapping/caba/source/src/mapping.cpp

CABA Constructor parameters

Mapping(

sc_module_name name, // Instance name

int ncycles) // Number of computation cycles

CABA Ports

- sc_in<bool> p_resetn : hardware reset

- sc_in<bool> p_clk : clock

- soclib::caba::FifoOutput<uint32_t> p_to_ctrl : interface from the mapping to the MWMR controller

- soclib::caba::FifoInput<uint32_t> p_from_ctrl : interface from the MWMR controller to the mapping

3) TLM-DT Implementation

a) Component definition & usage

Component definition

b) TLM-DT sources

- interface : source:trunk/soclib/soclib/module/ofdm_chain_components/mapping/tlmdt/source/include/mapping.h

- implementation : source:trunk/soclib/soclib/module/ofdm_chain_components/mapping/tlmdt/source/src/mapping.cpp

TLM-DT Constructor parameters

Mapping(sc_core::sc_module_name name, // Instance name uint32_t id, uint32_t read_fifo_depth, // Depth of input buffer uint32_t write_fifo_depth, // Depth of output buffer uint32_t n_read_channels, // Number of read channels uint32_t n_write_channels, // Number of write channels uint32_t n_config, // Number of configurations uint32_t n_status); // Number of status

TLM-DT Ports

- std::vector<tlm_utils::simple_target_socket_tagged<Mapping,32,tlm::tlm_base_protocol_types> *> p_config: configuration port

- std::vector<tlm_utils::simple_target_socket_tagged<Mapping,32,tlm::tlm_base_protocol_types> *> p_status: status port

- std::vector<tlm_utils::simple_initiator_socket_tagged<Mapping,32,tlm::tlm_base_protocol_types> *> p_read_fifo: port from the MWMR controller to the mapping

- std::vector<tlm_utils::simple_initiator_socket_tagged<Mapping,32,tlm::tlm_base_protocol_types> *> p_write_fifo: port from the mapping to the MWMR controller

Attachments (1)

- mapping.png (8.9 KB ) - added by 17 years ago.

Download all attachments as: .zip